[中級の電子工作テスト]

CANONデジ一で遊ぶ

PIC24F RTCCでカレンダー

PICで赤外線通信

PICでシリアル通信

FT232RL変換モジュール

K型熱電対 AD595CQ

K型熱電対のテスト MAX6675

連枝でラダープログラム

連枝でステッピングモータ

各種デバイスのテスト

[シーケンス回路テスト]

リレーシーケンス

[車載用電子工作テスト]

電源の取り方

[PCBCAD]

EAGLE CAD

[掲示板]

電子工作のテスト工場BBS

[リンク]

工作お役立ちリンク集

[電子工作のテスト工場]

表紙[TOP]へ戻る

[電子工作系]

Sivanyan_Radioのブログ

(↑↑管理人のブログです)

GAMEってたのすぃー

電子回路実験教材の部屋 RLC

電子マスカット 必見[MP3]!

kunioのホームページ AVR+MP3

なひたふ電子

ワタヤンの日記

BLUE's electronics room

isi's 趣味の電子工作

獣医さんの電子工作とパソコン研究室

電子用語集Web

YS電子工作ラボ

(↑↑管理人のブログです)

[プログラム系]

信彦の家

[SNS]

電子工作の広場SNS

[写真]

シャッターを押した瞬間

|

FPGAの勉強をするには開発ボードを購入するのが手っ取り早くてよいです。 色々製品がありますが、機能とコストを考えると「DE0」が一番ではないでしょうか。 Digi-keyで1,3000円程なのが特に魅力的です。 ピンが引き出されただけの基板に数万出すならこのボードをお奨めします。  |

|

[-- 1 -----] DEOでVGAコネクタに接続されているK22ピンを使おうとするとエラーが出ます。 理由はK22ピンに割り付けられている機能を使うように設定されている為に起こるようです。 設定変更方法はQuartusIIで 「Assignment->Device->DevicepinOptions->Dual-PurposePins」 と進みます。。 ここでK22に割り当てられている「nCE0」を「use as regular I/O」に変更する事によりK22をI/Oピンとして利用出来るようになります。 [-- 2 -----] バージョンSP1でNiosIIのTargetConnectionでIDエラーが消えませんでした。SP2になってからはSP1でエラーが出ていたものをそのまま使用してもエラーが出なくなりました。 こちらの環境だけかも知れませんが、うまくいかない場合はバージョンも疑ってみるのもいいかも知れません。 |

|

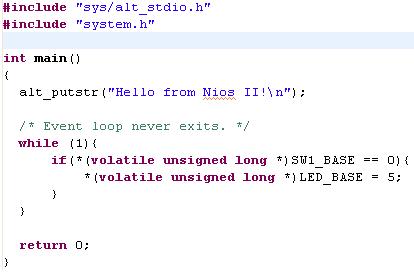

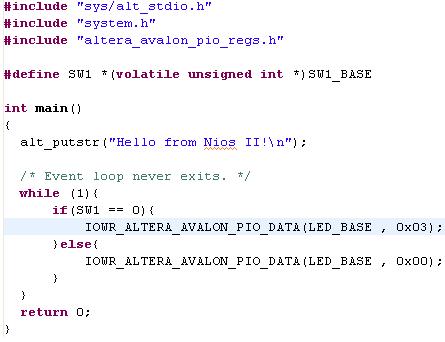

AlteraのFPGAの中にCPU(プロセッサ)を持たせると汎用性があがりとても便利になります。

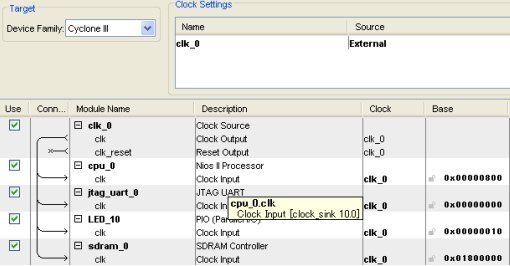

QuartsuIIでSOPC Builderというアプリを用いてCPUを構成し、CPUの入出力とFPGAの入出力をコンポーネントみたいに宣言して結合します。

何が出来たとかはSOPCが吐くファイルを見ればサンプルが出力されるのでそれをコピペして考えます。

あとはNiosIIでプログラムを書き、FPGAへダウンロードすればプログラムを実行する事ができます。

もちろんCPUを組んでも空いているところにロジックを組む事も出来ますし、内部で信号を繋ぐ事も可能です。

今回Niosを使おうと思ったのはDE0に搭載されているSD-RAMを使いたいからです。

自分でリフレッシュさせたりするのを考えるよりCPUに勝手にやってもらった方が(組み込まれると思う)楽だなぁという考えです。 CPUの構成方法ですが、既に絶版ですが「FPGA活用チュートリアル 2008/2009年版」をみて行いました。 Googleで検索してみると「Sim's blog」というブログさんに詳しく載っています。 記事はこちらの2つ http://blog.goo.ne.jp/sim00/e/8e1fc436d1e29a6decc20f8256adb914 http://blog.goo.ne.jp/sim00/e/35fbcf1fc1bfe67255e371c1ca2c770f 構成から動作確認までは行えると思います。 QuartusIIとNiosIIのバージョンがSP1の時はうまくいきませんでした。SP2になってからうまく動くようになりました。 こちらの環境だけかも知れませんが、参考までに書いておきます。 さて、DE0ボードに構築したCPUを書き込み動作チェックを行いました。LED0-9とSW0-2を使います。SW2をリセットスイッチとして、 SW1をプッシュスイッチ入力としています。今回はSW0は使っていません。SW1を押したらLEDが点灯し、話すと消えるというものを考えます。 またリセットスイッチ(SW2)を押すとNiosII上のコンソールに「Hello from Nios II!」と表示されます。 このコンソールへの表示は上で紹介した方法を一通り終えた後に消していない為に勝手に入っているものです。 I/Oのサンプル「1」  I/Oのサンプル「2」  以上で動作確認は完了とします。 Nios II エンベデッド・デザイン・スイートのサポート |

|

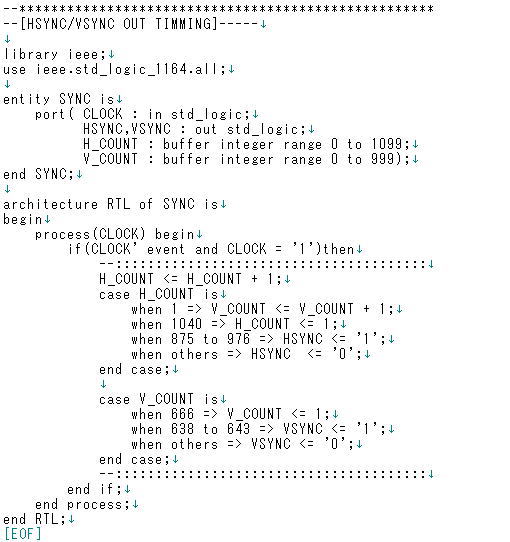

トランジスタ技術2009年11月号に画像表示に関して詳しく載っています。

マイコンを使う方法とCPLDを使う方法、その他いろいろ載っているので参考にして作業を進めました。 今回はDE0に乗っている50MHzがそのまま使える800x600表示を行います。P92に信号について載っています。 横(HSYNC)は800ドットですが、ブランキングというものが足されるので1040パルス、縦(VSYNC)はブランキングが足されて666パルスで1画面となります。 1040カウントして一段下がってを繰り返します。HSYNCが1040、VSYNCが666になったらもう一度頭からという感じで永遠に信号を出し続けなければなりません。 この辺りがマイコンよりPLDに向いているとろこではないでしょうか。 さて、ブランキング期間に同期信号を出してあげる必要があります。800x600の場合はHにする正論理ということです。HSYNCは857〜976まで、VSYNCは638〜644までをHiにすればよいようです。 そこで作成したブロックがこちら・・・(かっこよくないですが)  ブランキング期間はRGB信号を出してはいけません。 RGBがすべて0(Lo)では黒が出力されるので画面が真っ暗で何が表示されているかわかりません。 なのでクロックをカウントしてブランキング期間はRGB信号をOFF(全て0)にし、それ以外の期間はどこかのビット(RGB)をHiにすると画面に変化がでます。 結果は |

|

アルテラのFPGA内にCPUを組む場合、On-Chip Memoryで構成するサンプルが多くネットにありますが、

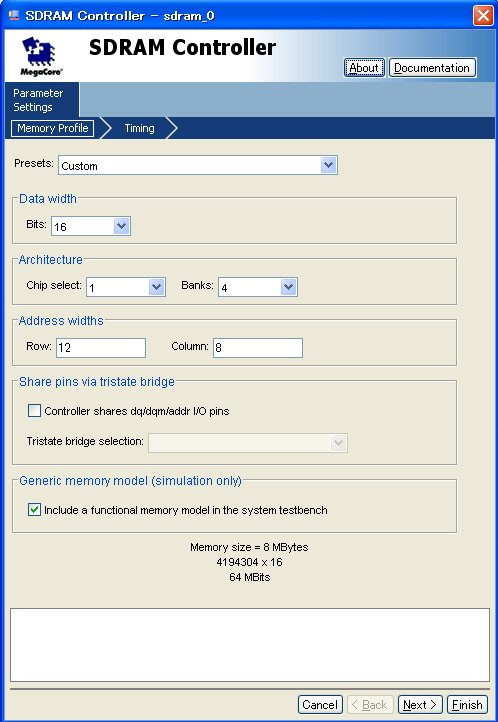

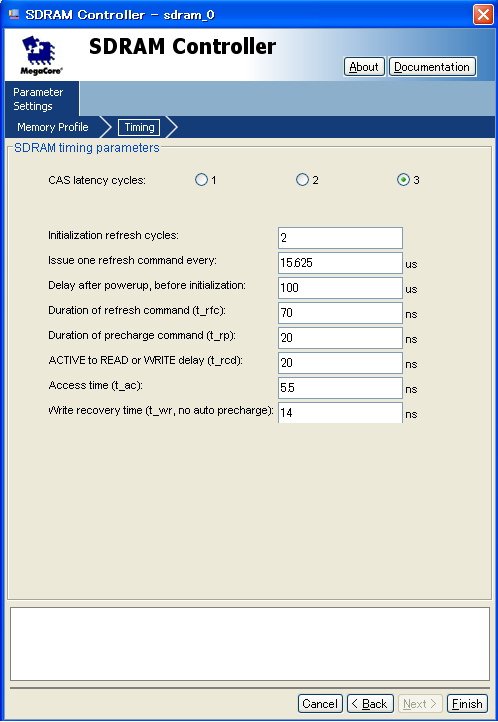

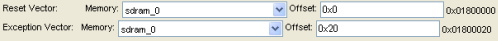

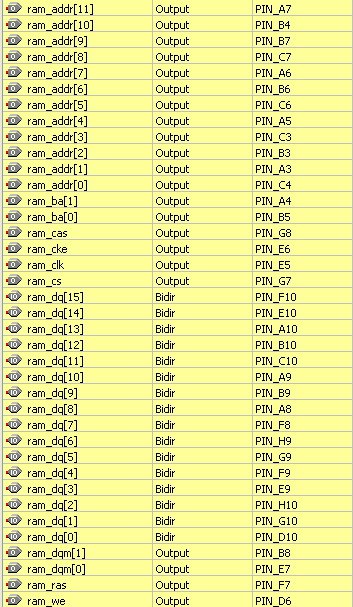

DE0にはSD-RAMが載っているのでこれを使って構成してみます。 SOPCでCPUを構成する方法は同じですが、On-Chip Memoriを選択せずにSDRAM Controllerを選択します。 Memories ans Memory Controllers -> SDRAM -> SDRAM Controller  追加されたsdramをダブルクリックすると現れるウィンドウの設定項目は次の通りです。   CPUの使用するメモリをSDRAMに設定します。  出来たサンプルファイルを確認し、VHDLを書きます。  最後の行はSDRAMへのクロック信号です。これがないと動きません。 ピンの設定はマニュアルを見ればわかりますが一応載せておきます。  これでプログラムが動きます。 |

Copyright (c) 2007-2022 amahime All Rights Reserved.